- English

- Español

- Português

- русский

- Français

- 日本語

- Deutsch

- tiếng Việt

- Italiano

- Nederlands

- ภาษาไทย

- Polski

- 한국어

- Svenska

- magyar

- Malay

- বাংলা ভাষার

- Dansk

- Suomi

- हिन्दी

- Pilipino

- Türkçe

- Gaeilge

- العربية

- Indonesia

- Norsk

- تمل

- český

- ελληνικά

- український

- Javanese

- فارسی

- தமிழ்

- తెలుగు

- नेपाली

- Burmese

- български

- ລາວ

- Latine

- Қазақша

- Euskal

- Azərbaycan

- Slovenský jazyk

- Македонски

- Lietuvos

- Eesti Keel

- Română

- Slovenski

- मराठी

- Srpski језик

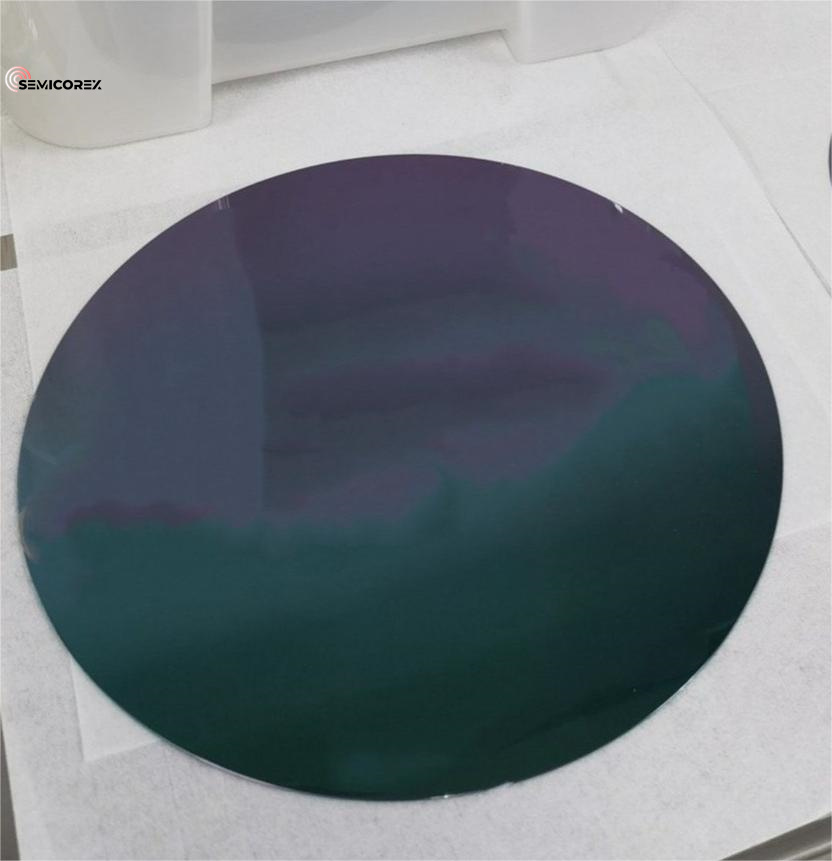

Silicio plokštelė

Silicio medžiaga yra kieta medžiaga, pasižyminti tam tikromis elektrinėmis puslaidininkių savybėmis ir fiziniu stabilumu, ir suteikia pagrindo atramą tolesniam integrinių grandynų gamybos procesui. Tai pagrindinė medžiaga silicio pagrindu pagamintiems integriniams grandynams. Daugiau nei 95% puslaidininkinių įtaisų ir daugiau nei 90% integrinių grandynų pasaulyje yra pagaminti ant silicio plokštelių.

Pagal skirtingus monokristalų auginimo būdus silicio pavieniai kristalai skirstomi į du tipus: Czochralski (CZ) ir plūduriuojančią zoną (FZ). Silicio plokšteles galima apytiksliai suskirstyti į tris kategorijas: poliruotas plokšteles, epitaksines plokšteles ir silicio izoliatorių (SOI).

Silicio poliravimo plokštelė reiškia asilicio plokštelėsusidaro poliruojant paviršių. Tai apvali plokštelė, kurios storis mažesnis nei 1 mm, apdorotas pjaustant, šlifuojant, poliruojant, valant ir kitais procesais iš vieno kristalo strypo. Jis daugiausia naudojamas integriniuose grandynuose ir atskiruose įrenginiuose ir užima svarbią vietą puslaidininkių pramonės grandinėje.

Kai V grupės elementai, tokie kaip fosforas, stibis, arsenas ir kt., yra legiruojami į silicio monokristalius, susidarys N tipo laidžios medžiagos; kai III grupės elementai, tokie kaip boras, yra legiruojami į silicį, susidaro P tipo laidžios medžiagos. Silicio monokristalų savitoji varža nustatoma pagal legiruotų dopingo elementų kiekį. Kuo didesnis dopingo kiekis, tuo mažesnė varža. Lengvai legiruoto silicio poliravimo plokštelės paprastai reiškia silicio poliravimo plokšteles, kurių savitoji varža didesnė nei 0,1 W·cm, kurios plačiai naudojamos didelės apimties integrinių grandynų ir atminties gamyboje; Stipriai legiruoto silicio poliravimo plokštelės paprastai reiškia silicio poliravimo plokšteles, kurių savitoji varža mažesnė nei 0,1 W·cm, kurios paprastai naudojamos kaip epitaksinių silicio plokštelių substrato medžiagos ir plačiai naudojamos puslaidininkių galios įtaisų gamyboje.

Silicio poliravimo plokštelėskurios sudaro švarų plotą ant paviršiaussilicio plokštelėspo atkaitinimo terminio apdorojimo vadinamos silicio atkaitinimo plokštelėmis. Dažniausiai naudojamos vandenilio atkaitinimo plokštelės ir argono atkaitinimo plokštelės. 300 mm silicio plokštelėms ir kai kurioms 200 mm silicio plokštelėms, kurioms keliami aukštesni reikalavimai, reikia naudoti dvipusį poliravimo procesą. Todėl sunku pritaikyti išorinę gavimo technologiją, kuri įveda gaudymo centrą per silicio plokštelės galinę dalį. Vidinis gavimo procesas, kurio metu naudojamas atkaitinimo procesas vidiniam gavimo centrui suformuoti, tapo pagrindiniu didelio dydžio silicio plokštelių gavimo procesu. Palyginti su įprastomis poliruotomis plokštelėmis, atkaitintos plokštelės gali pagerinti įrenginio veikimą ir padidinti našumą, todėl yra plačiai naudojamos skaitmeninių ir analoginių integrinių grandynų ir atminties lustų gamyboje.

Pagrindinis vieno kristalo augimo zonoje lydymosi principas yra pasikliauti lydalo paviršiaus įtempimu, siekiant sustabdyti išlydytą zoną tarp polikristalinio silicio strypo ir žemiau užauginto monokristalo, o pavienius silicio kristalus išvalyti ir auginti, judant išlydytą zoną aukštyn. Zonos lydymosi silicio monokristalai nėra užteršti tigliais ir yra labai gryni. Jie tinka N tipo silicio monokristalams (įskaitant neutronų transmutacija legiruotus pavienius kristalus), kurių savitoji varža didesnė nei 200Ω·cm, ir didelio atsparumo P tipo silicio monokristalams gaminti. Zonos lydymosi silicio monokristalai daugiausia naudojami aukštos įtampos ir didelės galios prietaisų gamyboje.

Silicio epitaksinė plokštelėreiškia medžiagą, ant kurios vienas ar keli plonos silicio monokristalinės plėvelės sluoksniai išauginami ant pagrindo epitaksiniu būdu nusodinant garų fazėje, ir daugiausia naudojama įvairiems integriniams grandynams ir atskiriems įrenginiams gaminti.

Pažangiuose CMOS integrinių grandynų procesuose, siekiant pagerinti vartų oksido sluoksnio vientisumą, pagerinti kanalo nuotėkį ir padidinti integrinių grandynų patikimumą, dažnai naudojamos silicio epitaksinės plokštelės, ty silicio plonos plėvelės sluoksnis. homogeniškai epitaksinis, auginamas ant lengvai legiruoto silicio poliruoto plokštelės, todėl galima išvengti didelio deguonies kiekio trūkumų ir daugelio bendrų siliciu poliruotų plokštelių paviršiaus defektų; tuo tarpu silicio epitaksinėms plokštelėms, naudojamoms galios integriniams grandynams ir atskiriems įrenginiams, didelės varžos epitaksinio sluoksnio sluoksnis paprastai yra epitaksinis, užaugintas ant mažos varžos silicio pagrindo (stipriai legiruoto silicio poliruoto plokštelės). Didelės galios ir aukštos įtampos taikymo aplinkoje maža silicio pagrindo varža gali sumažinti atsparumą įjungimui, o didelės varžos epitaksinis sluoksnis gali padidinti įrenginio gedimo įtampą.

SOI (silicio ant izoliatoriaus)yra silicis ant izoliacinio sluoksnio. Tai yra "sumuštinis" struktūra su viršutiniu silicio sluoksniu (Top Silicon), viduriniu silicio dioksido sluoksniu (BOX) ir silicio substrato atrama (rankena) apačioje. Kaip nauja substrato medžiaga integrinių grandynų gamybai, pagrindinis SOI privalumas yra tai, kad per oksido sluoksnį galima pasiekti aukštą elektros izoliaciją, kuri veiksmingai sumažins parazitinę talpą ir silicio plokštelių nuotėkį, o tai yra palanki aukštos kokybės greičio, mažos galios, didelės integracijos ir didelio patikimumo itin didelio masto integriniai grandynai, plačiai naudojami aukštos įtampos maitinimo įrenginiuose, optiniuose pasyviuosiuose įrenginiuose, MEMS ir kitose srityse. Šiuo metu SOI medžiagų paruošimo technologija daugiausia apima surišimo technologiją (BESOI), išmaniąją pašalinimo technologiją (Smart-Cut), deguonies jonų implantavimo technologiją (SIMOX), deguonies įpurškimo jungimo technologiją (Simbond) ir kt. Labiausiai paplitusi technologija yra išmanioji technologija. nuėmimo technologija.

SOI silicio plokštelėsgalima dar skirstyti į plonasluoksnes SOI silicio plokšteles ir storasluoksnes SOI silicio plokšteles. Plonos plėvelės viršutinio silicio storisSOI silicio plokštelėsyra mažesnis nei 1 um. Šiuo metu 95% plonasluoksnių SOI silicio plokštelių rinkos yra sutelkta 200 mm ir 300 mm dydžių, o rinkos varomoji jėga daugiausia yra didelės spartos, mažos galios gaminiai, ypač mikroprocesorių programose. Pavyzdžiui, pažangiuose procesuose, mažesniuose nei 28 nm, visiškai išeikvotas silicis ant izoliatoriaus (FD-SOI) turi akivaizdžių pranašumų: mažas energijos suvartojimas, apsauga nuo radiacijos ir atsparumas aukštai temperatūrai. Tuo pačiu metu SOI sprendimų naudojimas gali labai sumažinti gamybos procesą. Storosios plėvelės SOI silicio plokštelių viršutinis silicio storis yra didesnis nei 1 um, o palaidoto sluoksnio storis yra 0,5–4 um. Jis daugiausia naudojamas maitinimo įrenginiuose ir MEMS srityse, ypač pramoninio valdymo, automobilių elektronikos, belaidžio ryšio ir kt., Paprastai naudojami 150 mm ir 200 mm skersmens gaminiai.